好消息是 , 芯片设计工具带来的生产力提升也在以对数规模增长 。 这意味着在 2020 年代 , 你可以用一个人和一个工作站来设计芯片所做的事情是惊人的 。 如果 de Geus 和他的竞争对手的愿景成为现实 , 那么在 2030 年代很可能会非常惊人 。

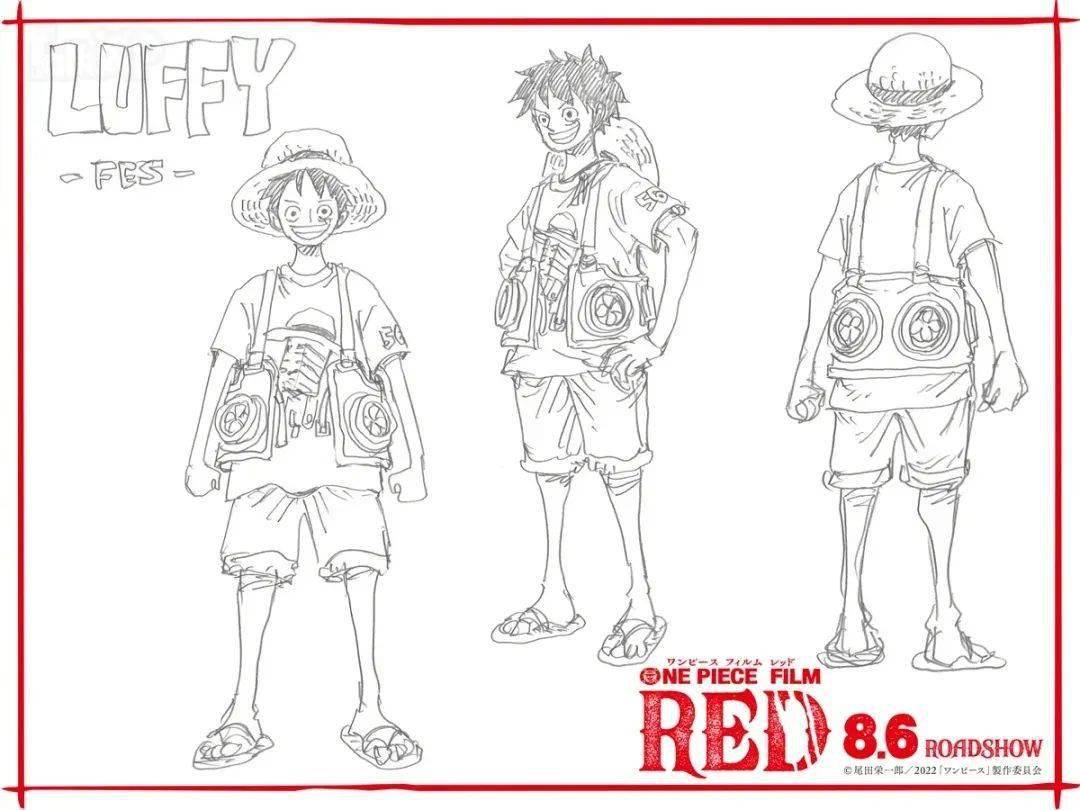

de Geus 说 , 在上图中 , Fusion 模块很重要 , 它在 Synopsys 工具链中称为 Fusion Compiler 的东西中实现 , 这是下一步的基础 , 即 DSO 。 Fusion 将所有这些不同的工具整合在一起以共享数据 , 因为设计人员可以优化芯片的功率、性能和面积——用术语来说是 PPA 。 这些不同的工具可以协同工作 , 但它们也会相互竞争 , 并且它们可以提供比以串行方式使用工具更优化的结果 。

1000 多个芯片设计的平均值 , 范围从 40 纳米到 3 纳米

借助 DSO , 机器学习嵌入到 Fusion Compiler 的所有单个元素中 , 模拟的输出用于驱动机器学习训练 , 而机器学习训练又用于驱动设计 。 我们设想这个的方式——de Geus 没有这么说——是 Synopsys 工具设计芯片和检查设计空间中的选项越多 , 它就会越快了解哪些有效 , 哪些无效 , 并且它会更好向人类芯片设计师展示如何推动他们的设计 。

DSO 早期阶段如何与 Synopsys 工具配合使用的示例

De Geus 强调了设计的重要部分 , 包括先前设计的基线和新设计的目标 。 一组人员使用 Synopsys 工具解决了这个问题 , 可以看到他们在功率和时间上都略微超过了客户目标 。 但随后 Synopsys 启动了 Fusion Compiler 及其 DSO AI 扩展 。 只需使用 DSO 对 Fusion 的扩展 , 就可以大大降低功耗并稍微向左一点 , 然后一旦启动 AI 训练的算法 , 功耗就会进一步降低 。 可以看到 DSO 和 DSO AI 仿真的“香蕉曲线” , 它允许设计人员沿着这些曲线权衡芯片上的功率和时序 。

2021年设计的实际 CPU 的另一次设计运行

一个专家团队花了几个月的时间来平衡 CPU 设计中的功率泄漏与时序 。 Fusion Compiler 的 DSO 扩展将其向左和向下推了一点 , 当打开该工具的 AI 训练模型时 , 一组新的漏电和时序选项被证明是可能的 。 与使用 Synopsys 工具的团队相比 , 一名工程师完成了 DSO 设计 , 并且该一名工程师能够获得的设计功耗降低 9% 到 13% , 漏电降低 30%——从 2 倍到 5 倍不等更快的设计完成时间 。

在将 AI 注入工具后 , 此类进步的主题演讲中还有更多示例 。 但事情就是这样 , de Geus 多次强调这一点 。 这些进步的累积性质不是相加的 , 而是相乘的 。 它们将比许多不同设计向量可能暗示的改进百分比放大得多 。

“开发编写 EDA 的计算机的手可以帮助开发下一台编写更好 EDA 的计算机 。 ”de Geus 在演讲结束时解释道 。 “那个圈子带来了指数级的成就 。 所以我们经常说成功是我们努力的总和 。 不 , 这不对 。 这是我们努力的产物 。 一个零 , 我们都会下沉 。 伟大的合作 , 我们都飞升了 。 ”

相关经验推荐

- 苹果|从手机芯片出发,搭载这三款旗舰芯片的手机最值得买

- iPhone|良率过低,iPhone 14无缘3nm芯片?

- 小米科技|猛料不断!被质疑是“套娃”设计,小米到底能不能自己造芯片?

- 芯片|芯片出货量排名:华为已经落后,高通无缘第一,第三名有点厉害!

- OPPO|OPPO把联发科芯片手机卖苹果13的价格,低配高价还是物有所值?

- 芯片|进入酷睿11代后性能提升惊人,3000元价位的i3笔记本能买吗?

- 华为mate50|华为Mate50再被官方确认,4nm芯片+新系统,外观、价格等信息量大

- 华为鸿蒙系统|7nm麒麟芯片+AI四摄,跌至1381元,鸿蒙系统手机也很便宜

- 芯片|国产17nm工艺内存芯片良率已达40% Q2首发供应DDR4

- 红米手机|Redmi K50 Pro配置揭晓:搭载联发科天玑8100芯片!