文章图片

文章图片

文章图片

文章图片

文章图片

文章图片

芯片设计既是一门艺术 , 也是一项极为复杂的工程 , 并且设计的风险和研发成本也越来越高昂 。

据IBS首席执行官Handel Jones介绍 , 目前“成功研发一款28nm芯片的平均成本为4000万美元 , 相比之下 , 7nm芯片的成本为2.17亿美元 , 5nm芯片的成本为4.16亿美元 , 3nm芯片的成本将高达5.9亿美元 。 ”显然 , 随着工艺制程节点的提升 , 研发一款芯片如果失败 , 其成本将会越来越高 。

但是 , 由于逻辑和存储区块的所有可能布局以及连接它们的导线 , 存在看似无限的布局组合 , 而且通常 , 不管你信不信 , 芯片布局规划中最优秀的设计人员都是根据经验和预感工作的 , 他们不能总是给出一个很好的答案 , 来说明为什么特定模式有效、而其他模式无效 。

因此 , 研究人员也一直在尝试将人类的猜测以及一些重复性的工作 , 从这项芯片设计任务中剔除 , 并朝着更优化的设计迈进 。 即便是随着Chiplet设计的“火爆” , 这项任务也不会消失 , 因为计算引擎上的所有小芯片都需要互连才能成为虚拟单片芯片 , 并且必须考虑所有延迟和功耗对此类电路复合体的影响 。

因此 , 将人工智能(AI)技术引入到帮助加速芯片设计 , 也是一项很自然的事情 。

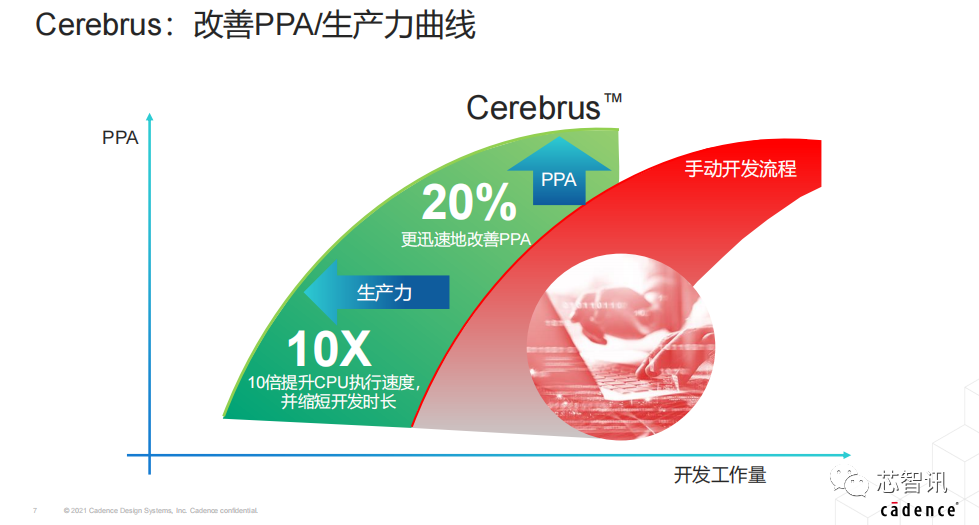

EDA厂商引入AI加速芯片设计

早在2020年 , 芯片设计所需的EDA工具大厂新思科技(Synopsys.)就推出了业界首个用于芯片设计的自主人工智能应用程序——DSO.ai?(Design Space Optimization AI) 。 作为一款人工智能和推理引擎 , DSO.ai能够在芯片设计的巨大求解空间里搜索优化目标 。

三星设计平台开发部执行副总裁Jaehong Park当时就表示:“在我们的设计环境中 , 新思科技DSO.ai能系统地找到最佳解决方案 , 从而在我们已经实现的PPA(性能、功耗与面积)优化成果上实现更进一步的突破 。 此外 , 原本需要多位设计专家耗时一个多月才可完成的设计 , DSO.ai只要短短3天即可完成 。 这种AI驱动的设计方法将使三星的用户能够在芯片设计中充分利用我们先进技术的优势 。 ”

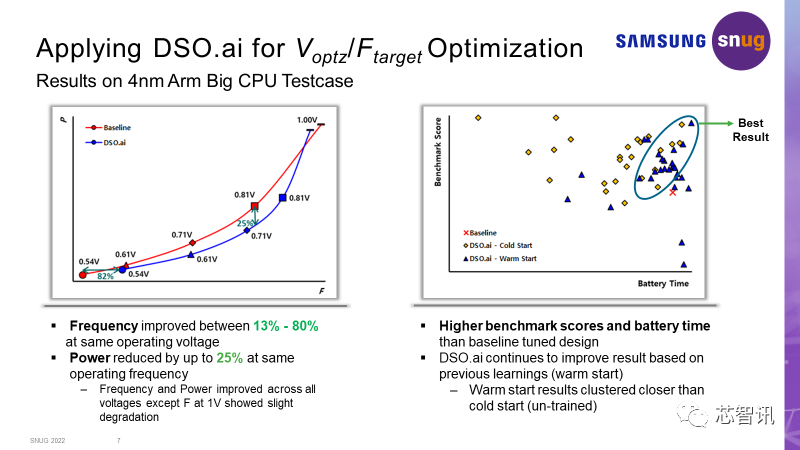

新思科技今年6月底最新公布的资料显示 , 在三星的案例中 , DSO.ai技术被成功应用于开发Voptz和Ftarget优化应用程序 , 通过自动探索大量的电压(V)/目标频率(F)空间以找出最高基准分数和最长电池时间的最佳组合 。 此外 , DSO.ai RL模型将通过分析之前运行中的选择 , 自动学习并生成更好的组合 。 这也使得三星在4nm Arm Big CPU利用DSO.ai设计 , 在相同的工作电压下 , 实现了频率提升13%-80%;而在相同的工作频率下 , 最高可将功耗降低25% 。

【芯片设计|谷歌、英伟达及EDA厂商纷纷下场,AI如何改变芯片设计?】

索尼也在设计传感器的过程也利用DSO.ai技术并验证了其出众的性能 。 与专家工程师的人工操作相比 , DSO.ai实现最佳结果仅需1/4的设计周期、1/5的设计工作量 , 并成功将功耗降低了3% , 进一步提升设计结果质量 。

相关经验推荐

- it芯片|千年等一回!!!279元秒杀到手16GB(8G*2)内存套装

- 键盘|华为P60Pro概念机:就算再晚1年发布,没有麒麟芯片也劝你买一台

- AMD|5000mAh大电池+67W闪充,荣耀70Pro同款芯片,售价仅1599元

- 小米科技|从4699降至3159元,三主摄+自研充电芯片,小米旗舰加速退场!

- |曾经的ColorOS系统竟长这样?绿厂设计加分,8月30日相约水生万物

- 芯片|目前这3部手机值得买,几乎“零”差评,用到2026年不成问题

- ColorOS|ColorOS 13正式版设计曝光!注入生命力?

- 华为|四方芯片联盟合围国产芯片,这次到了“图穷匕见”的关键时刻

- 三星Galaxy|美芯片法案正式签署,中国芯退无可退,“第二个华为”出招了?

- 芯片|轻薄型移动工作站值与不值,从戴尔Precision 5470说起……